《CMOS集成电路后端设计与实战》 刘峰倾力之作,机械工业出版社助您掌握IC设计核心

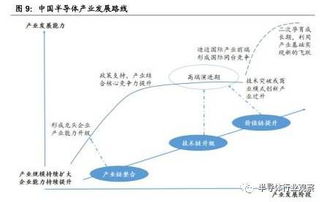

在当今信息技术飞速发展的时代,集成电路(IC)作为电子设备的“大脑”,其设计与制造水平直接关乎国家科技实力与产业竞争力。其中,CMOS技术凭借其低功耗、高集成度等优势,已成为主流工艺。而集成电路设计流程中的后端设计,更是将电路逻辑转化为实际物理版图的关键环节,技术壁垒高、实践性强。由刘峰编著、机械工业出版社出版的《CMOS集成电路后端设计与实战》一书,正是一部系统深入、注重实战的权威指南,为有志于深入该领域的工程师、学者和学生提供了宝贵的学习资源。

本书作者刘峰在集成电路设计领域拥有深厚的理论功底和丰富的工程实践经验。他敏锐地捕捉到行业对后端设计实战人才的迫切需求,以及现有教材中理论与实践结合不足的缺口,从而撰写了这部著作。机械工业出版社作为国内知名的科技类图书出版机构,以其严谨的学术态度和高标准的出版质量,确保了本书内容的权威性与准确性。

《CMOS集成电路后端设计与实战》的内容结构清晰,循序渐进。全书大致可分为三大部分:

第一部分:基础理论夯实

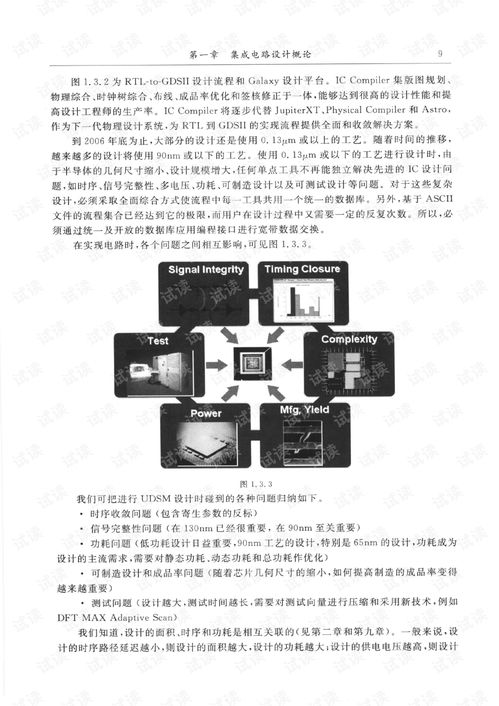

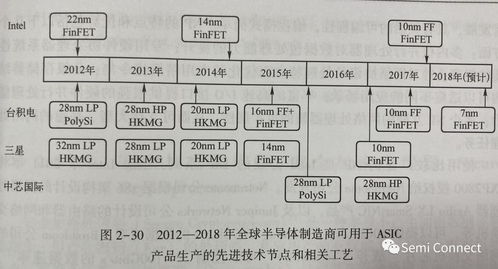

开篇系统回顾了CMOS集成电路的基本原理与制造工艺,为后续的后端设计学习奠定坚实的物理基础。重点讲解了MOS晶体管特性、CMOS反相器及基本逻辑门电路,并介绍了深亚微米及纳米工艺下面临的挑战,如互连延迟、功耗、信号完整性等核心问题。

第二部分:后端设计流程精解

这是本书的核心精华所在。作者以工业界标准设计流程为主线,详细剖析了后端设计的每一个关键步骤:

- 逻辑综合与优化:如何将RTL代码转换为门级网表,并进行面积、时序和功耗的优化。

- 布图规划与布局:包括芯片大小规划、模块布局、电源规划(电源网格设计)以及I/O布局,目标是优化面积、时序和布线拥塞。

- 时钟树综合:深入讲解如何构建低偏斜、低功耗的全局时钟分布网络,这是确保芯片同步性能的重中之重。

- 布线:详细阐述全局布线与详细布线策略,解决信号互联、满足时序约束并规避设计规则检查(DRC)错误。

- 物理验证与签核:涵盖设计规则检查(DRC)、版图与电路图一致性检查(LVS)、电气规则检查(ERC)以及静态时序分析(STA)和功耗分析等最终确认环节。

第三部分:实战案例与高级议题

本书尤为突出的亮点是“实战”部分。作者通过精心设计的完整项目案例,带领读者使用主流EDA工具(如Synopsys, Cadence等平台)从头至尾完成一个模块或小型芯片的后端设计过程。这极大地弥合了理论与工程实践之间的鸿沟。本书还探讨了当前业界关注的高级议题,如低功耗设计技术(多电压域、电源门控)、可制造性设计(DFM)、片上系统(SoC)集成后端挑战等,拓宽了读者的视野。

本书特色与价值

1. 体系完整,循序渐进:从基础到前沿,从理论到实践,构建了完整的CMOS后端设计知识体系。

2. 侧重工程,实战性强:大量的操作步骤、实例截图、脚本示例和问题分析,极具可操作性,能有效提升读者解决实际工程问题的能力。

3. 反映业界最新实践:内容紧密结合当前主流的深亚微米/纳米工艺和EDA工具流,保证了所学知识的时效性和实用性。

4. 权威出版,质量保障:机械工业出版社的背书,确保了图书内容的严谨和专业。

适合读者

- 高等院校微电子、集成电路设计相关专业的高年级本科生和研究生。

- 初入集成电路行业的后端设计工程师,用于系统学习和快速上手。

- 前端设计、验证等其他相关岗位的工程师,希望深入了解后端流程以加强团队协作。

- 对集成电路物理设计有兴趣的科研人员和技术爱好者。

总而言之,《CMOS集成电路后端设计与实战》是一部不可多得的优秀专业书籍。它不仅仅是一本教材,更是一位经验丰富的“工程师导师”。通过研读本书,读者能够系统掌握CMOS集成电路后端设计的全流程核心技术与实战技能,为在集成电路这一尖端领域深耕发展打下坚实的基础,为我国IC设计产业的自主创新与人才培养贡献一份力量。

如若转载,请注明出处:http://www.fushanmingchuang.com/product/99.html

更新时间:2026-04-19 23:50:42