模拟集成电路设计 从理论到实践的核心指南

模拟集成电路(Analog IC)设计是电子工程领域中一门既复杂又充满艺术性的学科,它专注于处理连续变化的电压和电流信号。与数字集成电路处理离散的“0”和“1”不同,模拟电路直接与真实世界(如声音、光线、温度、压力)的连续信号交互,因此其设计对噪声、非线性、功耗和工艺偏差极为敏感。本文旨在为初学者和有经验的设计者提供一个核心指南,涵盖设计流程、关键模块与最佳实践。

一、 设计流程概览

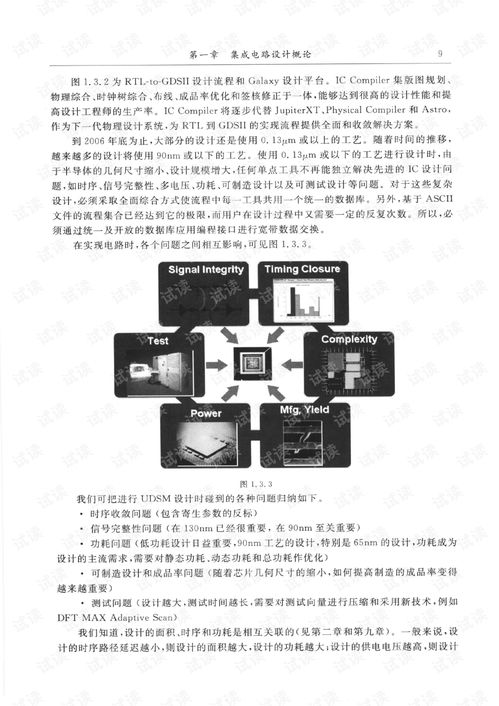

一个典型的模拟IC设计遵循系统化的流程:

- 需求分析与系统规划:明确电路规格,如增益、带宽、功耗、电源电压、噪声系数、线性度(如IIP3)、工艺节点等。这些是设计成败的基石。

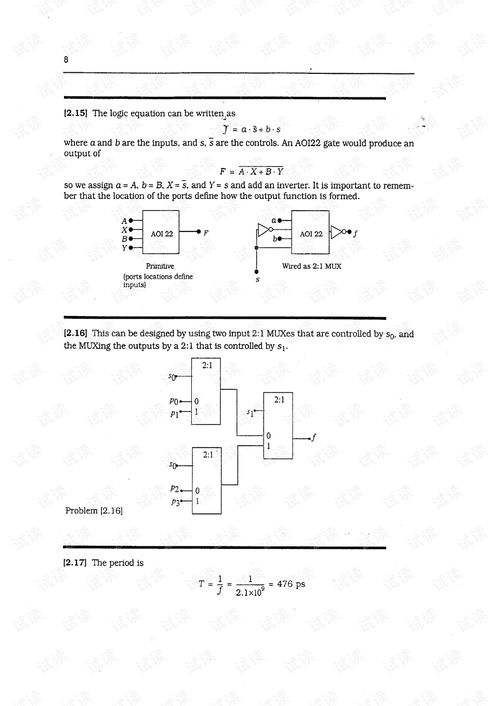

- 架构选择与拓扑设计:根据规格选择合适的电路架构,例如运算放大器(Op-Amp)是采用折叠共源共栅、两级米勒补偿还是轨到轨结构?这需要深入理解各种拓扑的优缺点。

- 晶体管级设计:这是设计的核心。确定每个MOSFET或BJT的尺寸(W/L)、偏置点,通过手工计算(如平方律模型、gm/Id方法)结合EDA工具的仿真来满足性能指标。

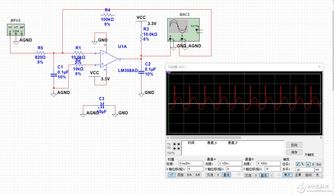

- 仿真与验证:使用SPICE类工具(如Cadence Spectre, HSPICE)进行深入的仿真分析,包括:

- 直流(DC)分析:确定工作点。

- 交流(AC)分析:评估频率响应、增益和相位裕度(稳定性)。

- 瞬态(Transient)分析:观察时域响应和大信号行为。

- 噪声(Noise)分析:量化电路引入的噪声。

- 工艺角(Corner)与蒙特卡洛(Monte Carlo)分析:评估制造工艺波动和器件失配对性能的影响,确保设计的鲁棒性。

- 版图设计:将电路图转化为物理掩模图形。模拟版图是艺术与科学的结合,必须精心处理匹配、噪声隔离(保护环)、寄生效应、电流密度和天线效应等问题。

- 后仿真:提取版图的寄生电阻电容(RC Extraction)后,再次进行仿真,验证物理实现是否仍满足所有规格。

- 流片与测试:将设计数据(GDSII)送至晶圆厂制造,芯片返回后进行实际测试,与仿真结果对比。

二、 关键模块与设计要点

- 运算放大器(Op-Amp):模拟设计的“工作马”。核心指标包括开环增益、单位增益带宽(GBW)、相位裕度、压摆率、输入/输出摆幅、共模抑制比(CMRR)和电源抑制比(PSRR)。设计时常在增益、带宽、功耗和面积之间进行折衷。

- 偏置电路:为整个芯片提供稳定、与工艺和温度变化无关的参考电流/电压。带隙基准(Bandgap Reference)是最核心的模块之一。

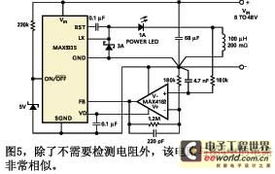

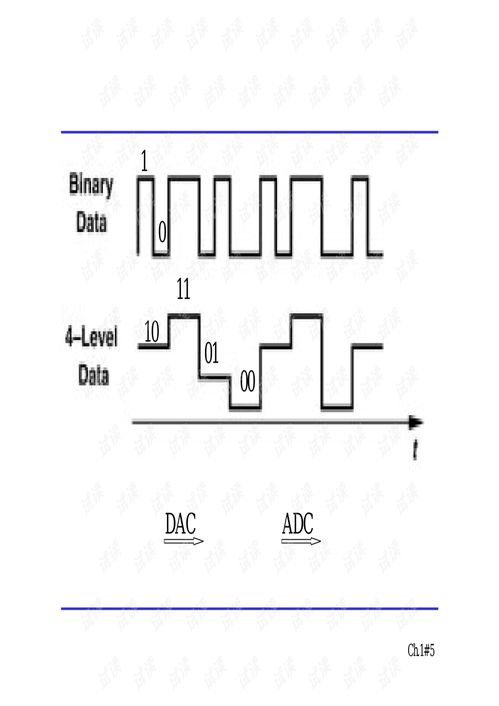

- 数据转换器:连接模拟与数字世界的桥梁。

- 模数转换器(ADC):如逐次逼近型(SAR)、流水线型(Pipeline)、Σ-Δ型,各有其速度、精度和功耗的权衡。

- 数模转换器(DAC):如电流舵型、电阻/电容阵列型。

- 锁相环(PLL)与时钟电路:用于频率合成和时钟恢复,包含鉴相器、电荷泵、环路滤波器和压控振荡器(VCO)等关键子模块。相位噪声和抖动是关键指标。

三、 核心挑战与设计哲学

- 噪声管理:热噪声、闪烁噪声(1/f噪声)是模拟电路的天敌。设计中需通过增大器件尺寸、采用共源共栅结构、合理滤波等方式抑制噪声。

- 匹配性:差分对、电流镜等对器件匹配要求极高。版图上必须采用共质心、交叉耦合等布局技术,并注意环境梯度(如温度、应力)的一致性。

- 电源与衬底噪声隔离:在混合信号芯片中,数字开关噪声会通过电源线和衬底耦合到敏感的模拟部分。设计中必须使用独立的电源轨、深N阱隔离、保护环和片上去耦电容。

- 仿真与现实的鸿沟:SPICE模型并非完美,尤其是纳米级工艺下,二阶、三阶效应显著。设计者必须理解模型局限,预留足够的设计余量(Margin)。

四、 工具与技能

现代模拟IC设计高度依赖EDA工具链(如Cadence, Synopsys, Mentor Graphics),但工具的熟练使用不能替代扎实的半导体物理、器件模型和电路理论功底。一名优秀的模拟设计师既是科学家,也是工程师,需要具备直觉、耐心和解决问题的创造力。

###

模拟集成电路设计是一条充满挑战但回报丰厚的道路。它要求设计者对电子学的基本原理有深刻的理解,并具备在复杂约束下进行优化和折衷的能力。随着工艺节点的不断演进和系统集成度的提高,模拟设计的角色非但没有减弱,反而变得更加关键。持续学习、动手实践并从每一次流片(无论成功与否)中汲取经验,是通往精通的唯一途径。

如若转载,请注明出处:http://www.fushanmingchuang.com/product/98.html

更新时间:2026-04-15 15:15:21