单电源集成电路开关稳压器的设计原理与实现分析

引言

在现代电子系统中,电源管理单元(PMU)是确保系统稳定、高效运行的核心。其中,开关稳压器(Switch Mode Power Supply, SMPS)凭借其高效率、小体积和宽输入电压范围等优势,已成为集成电路(IC)电源设计的首选方案。特别是单电源输入的开关稳压器IC,因其设计简洁、外围元件少,被广泛应用于便携设备、嵌入式系统及各类消费电子中。本文将深入分析基于单电源的集成电路开关稳压器的电路设计原理、关键模块构成、性能考量以及设计挑战。

一、 单电源开关稳压器的基本原理

开关稳压器的核心工作原理是利用功率开关管(通常为MOSFET)的高频导通与截止,配合电感、电容等储能元件,通过脉冲宽度调制(PWM)或脉冲频率调制(PFM)来控制能量传递,从而实现高效的电能转换与稳压。

对于单电源设计,意味着整个IC仅需一个输入电源(如电池或适配器输出的直流电压),通过内部电路产生所有必要的偏置电压(如栅极驱动电压、内部逻辑电源),并完成从输入到期望输出电压的转换。常见的拓扑结构包括:

- 降压型(Buck):输出电压低于输入电压。这是应用最广泛的拓扑。

- 升压型(Boost):输出电压高于输入电压。

- 升降压型(Buck-Boost):输出电压可低于或高于输入电压。

二、 集成电路内部关键模块设计分析

一颗典型的单电源开关稳压器IC集成了多个功能模块,其协同工作是实现高性能的关键。

1. 功率级(Power Stage)

这是能量转换的核心。在单片IC中,通常集成了:

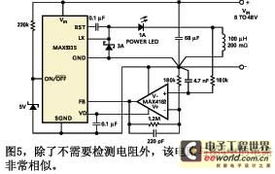

- 功率开关管(Power MOSFET):包括上管(High-side)和下管(Low-side)。对于同步整流架构,两者均为MOSFET;对于非同步架构,下管为肖特基二极管。设计时需在导通电阻(Rds(on))、开关速度、芯片面积和成本之间取得平衡。

- 栅极驱动器(Gate Driver):为功率管的栅极提供足够强且快速的充放电电流,以减小开关损耗。驱动器本身需要一个高于输入电压的“自举”(Bootstrap)电源来驱动上管,这是单电源设计中一个需要巧妙处理的问题。

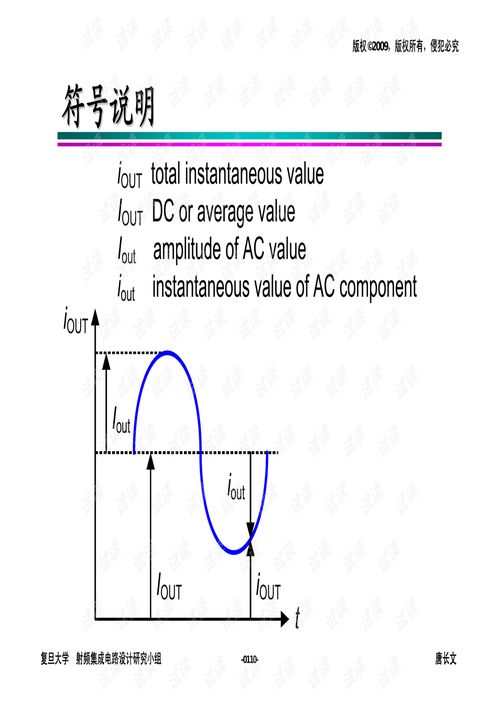

2. 控制与调制模块

- 误差放大器(Error Amplifier):将反馈电压(通常来自输出电压的分压)与内部精密基准电压(如带隙基准)进行比较,产生误差信号。

- PWM/PFM调制器:根据误差信号生成占空比可变的脉冲信号,控制功率管的开关。为兼顾轻载效率,现代IC常采用PWM/PFM自动切换模式。

- 振荡器(Oscillator):产生恒定频率的锯齿波或时钟信号,作为PWM的时基。频率选择(通常在数百kHz至数MHz)需权衡效率、体积(外围电感电容大小)和电磁干扰(EMI)。

3. 保护与辅助电路

- 过流保护(OCP):通过检测下管电流或电感电流峰值,防止芯片和负载损坏。

- 过温保护(OTP):集成温度传感器,在结温过高时关闭输出。

- 欠压锁定(UVLO):确保输入电压达到一定阈值后芯片才启动,防止工作异常。

- 软启动(Soft-start):控制启动时的占空比缓慢增加,抑制输入浪涌电流。

- 内部低压差线性稳压器(LDO):为芯片内部的模拟和数字电路(如基准、误差放大器、逻辑控制)提供一个干净、稳定的低压电源,通常由输入电压或输出电压衍生而来。

三、 单电源设计的特殊考量与挑战

1. 自举电源的生成

在降压拓扑中,驱动上管NMOS需要栅极电压高于源极电压(即开关节点电压)。单电源下,通常采用“自举电路”:利用一个二极管和电容,在下管导通期间,从输入电源(VIN)或内部LDO输出(VCC)为电容充电,从而在上管需要导通时提供一个浮动的驱动电压(VBS)。该电路的设计直接影响高压侧驱动的可靠性和效率。

2. 高效率与低静态电流的平衡

对于电池供电设备,轻载和待机效率至关重要,这就要求控制电路本身的静态电流(Quiescent Current, IQ)极低。这给模拟电路(如基准源、误差放大器)的设计带来了挑战,需要在极低功耗下仍保持良好的精度和响应速度。

3. 热管理与封装

功率损耗(主要是开关管导通损耗和开关损耗)会导致芯片温升。在单芯片集成中,必须精心规划功率管、驱动器和控制电路的版图布局,优化散热路径。封装的选择(如QFN、DFN等具有裸露焊盘(Exposed Pad)的封装)对散热性能影响巨大。

4. 电磁兼容性(EMI)抑制

开关动作产生的高频di/dt和dv/dt是主要的EMI源头。在IC内部设计中,可以采用:

- 栅极驱动斜率控制,减缓开关边沿。

- 扩频调制技术,将开关能量分散在更宽的频带上。

- 优化的功率回路版图布局,最小化寄生电感。

四、 设计流程与仿真验证

现代开关稳压器IC的设计是一个高度系统化的过程:

- 系统定义:明确输入电压范围、输出电压/电流、效率目标、保护功能等规格。

- 拓扑选择与电路设计:确定功率级参数(电感、电容计算)、设计各个模拟和数字模块的子电路。

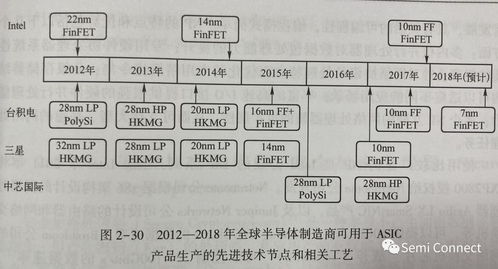

- 晶体管级实现与版图设计:使用CMOS或BCD工艺,进行器件选型、电路绘制,并特别关注功率路径、敏感模拟信号(如反馈、基准)的隔离与屏蔽。

- 综合仿真验证:利用SPICE等工具进行直流、交流、瞬态、蒙特卡洛以及温度扫描仿真,验证功能、效率、负载调整率、线性调整率、瞬态响应等关键指标。

- 样片测试与迭代:流片后在实际PCB上进行全面测试,评估其真实性能,并根据结果进行设计优化。

结论

单电源集成电路开关稳压器的设计是模拟与功率集成电路领域的经典课题。它要求设计者深刻理解开关电源原理、半导体器件特性、模拟电路设计以及热力学和电磁学知识。随着工艺进步(如更先进的BCD工艺)和设计技术发展,未来的单电源开关稳压器IC将朝着更高效率(尤其是轻载效率)、更高功率密度、更高集成度(集成更多功率管、甚至电感)、更智能的数字控制以及更优越的EMI性能方向持续演进,为日益复杂和节能的电子系统提供强劲而精密的“心脏”。

如若转载,请注明出处:http://www.fushanmingchuang.com/product/97.html

更新时间:2026-04-10 22:56:46