专用集成电路设计实用教程 从概念到流片的系统指南

第一章:专用集成电路设计概述

专用集成电路(ASIC)是为特定应用或客户量身定制的集成电路,与通用处理器(如CPU)相比,它能通过硬件优化提供更高的性能、更低的功耗和更小的面积。ASIC设计是一个复杂的系统工程,涉及算法、架构、电路、物理实现和验证等多个层面。

第二章:设计流程与工具链

一个典型的ASIC设计流程包括以下几个关键阶段:

- 规格定义:明确芯片的功能、性能、功耗、面积和接口等指标,形成详细的设计规范文档。这是所有后续工作的基石。

- 架构设计:根据规格,进行高层次建模和算法验证(通常使用C/C++、SystemC或MATLAB),确定芯片的整体架构、模块划分和关键数据通路。

- 前端设计(RTL级):使用硬件描述语言(Verilog或VHDL)将架构转化为寄存器传输级(RTL)代码。此阶段的核心是功能正确性,需进行大量的仿真和形式验证。

- 逻辑综合:使用综合工具(如Synopsys Design Compiler),将RTL代码、工艺库和约束(时序、面积、功耗)作为输入,生成门级网表。

- 后端设计(物理实现):这是将逻辑网表转化为物理版图的过程,主要包括:

- 布局规划:规划芯片整体面积、模块位置及I/O排列。

- 布局:放置标准单元和宏模块。

- 时钟树综合:构建低偏差、低延时的全局时钟网络。

- 布线:完成单元之间所有信号的金属连线。

- 物理验证:进行设计规则检查(DRC)、版图与原理图对照(LVS)以及电气规则检查(ERC),确保版图符合晶圆厂要求且与网表一致。

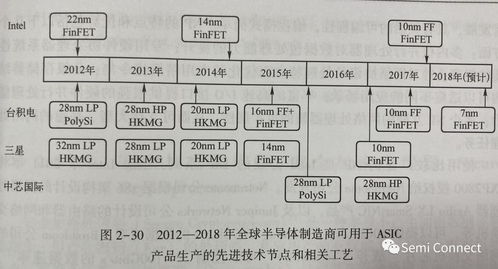

- 流片与测试:将最终确认的版图数据(GDSII格式)交付给晶圆厂制造。芯片返回后,进行全面的硅后测试和验证。

常用工具来自三大EDA巨头:Synopsys、Cadence和Siemens EDA(原Mentor Graphics)。

第三章:实用设计方法与技巧

- 可综合编码风格:编写RTL代码时,必须时刻考虑其可综合性和硬件可实现性,避免使用不可综合的结构(如

#delay、initial块用于逻辑生成)。推荐使用同步设计、清晰的有限状态机(FSM)和模块化设计。 - 低功耗设计:功耗是现代芯片设计的核心约束。实用技术包括:

- 时钟门控:在寄存器不工作时关闭时钟,动态降低动态功耗。

- 多电压域:为不同性能要求的模块提供不同的工作电压。

- 电源门控:关闭空闲模块的电源,彻底消除其静态功耗和动态功耗。

- 时序收敛:确保芯片在所有工艺角(PVT:工艺、电压、温度)和模式下都能满足时序要求。关键在于设置合理的时序约束,并在布局布线阶段进行迭代优化。

- 可测性设计:为了在生产后高效测试芯片,必须提前插入可测性结构,最常用的是扫描链(Scan Chain)和边界扫描(JTAG)。

第四章:验证策略

验证是确保芯片功能正确的生命线,其工作量通常占整个项目的70%以上。一个完善的验证策略包括:

- 仿真验证:使用UVM(通用验证方法学)等搭建模块级和系统级的定向测试与随机约束测试平台。

- 形式验证:使用数学方法穷尽证明设计在某些属性上的正确性,常用于关键控制逻辑和等价性检查(RTL vs. 网表)。

- 硬件仿真与原型验证:使用FPGA或专用硬件仿真器(如Palladium, Zebu)搭建接近真实速度的验证环境,进行软硬件协同验证和早期软件开发。

第五章:项目管理与团队协作

ASIC设计是团队作业,需要高效的项目管理。使用版本控制系统(如Git)管理代码和文档,建立清晰的代码和设计评审流程,制定详细且可追踪的项目计划(通常使用甘特图),并管理好来自晶圆厂不断更新的工艺文件和数据。

###

专用集成电路设计是知识、经验与工具的深度结合。成为一名优秀的ASIC工程师,不仅需要扎实的数字电路、计算机体系结构和半导体物理基础,更需要通过实际项目不断磨练,深入理解从系统需求到硅晶片的完整链条。本教程旨在提供一个系统性的实用框架,真正的精通始于动手实践,并伴随着每一次的流片成功与失败后的复盘。

如若转载,请注明出处:http://www.fushanmingchuang.com/product/96.html

更新时间:2026-04-10 06:05:45