探秘芯片诞生记 集成电路设计全流程科普

集成电路(Integrated Circuit, IC),常被称为芯片,是现代电子设备的心脏。从智能手机到航天器,无处不在的芯片背后,是一套精密而复杂的设计流程。今天,我们就来一起揭开集成电路设计的神秘面纱,看看一颗芯片是如何从概念走向现实的。

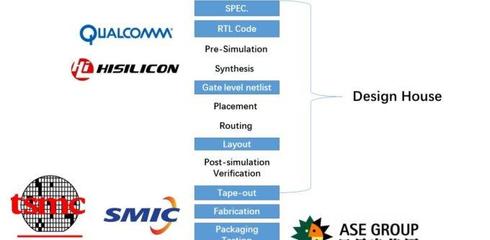

集成电路设计,通常称为IC设计,是一个将系统、逻辑与性能要求转化为具体物理版图的过程,最终交付给芯片制造厂(Foundry)进行生产。整个流程可以被形象地比喻为建造一座超微型、结构极其复杂的“城市”。这个过程主要分为前端设计和后端设计两大阶段,并遵循着从抽象到具体、从功能到物理的实现路径。

第一阶段:前端设计——定义芯片的“灵魂”与“大脑”

前端设计关注芯片的功能、架构和逻辑,核心目标是产出芯片的“电路原理图”。

- 系统规格定义:这是设计的起点。工程师需要明确芯片的用途、性能指标(如速度、功耗)、成本目标以及需要符合的行业标准。这相当于为整个项目制定一份详尽的“需求说明书”。

- 架构设计:基于规格,设计团队规划芯片的整体架构。这包括决定使用哪些核心模块(如CPU核、GPU核、内存控制器等)、模块之间如何互联(总线结构)、以及如何进行功耗管理和时钟分配。此时会搭建系统级模型进行初步验证。

- 逻辑/电路设计:

- RTL设计:工程师使用硬件描述语言(HDL,如Verilog或VHDL),以代码的形式描述芯片各模块在寄存器传输级(RTL)的行为。这段代码精确规定了数据如何在寄存器之间流动和处理,是设计的核心成果之一。

- 功能验证:通过仿真工具,对RTL代码进行大量的测试,确保其功能完全符合最初的设计规格。这一步会找出逻辑错误,是保证芯片“思想正确”的关键。

- 逻辑综合:利用电子设计自动化(EDA)工具,将经过验证的RTL代码,结合目标工艺库(由芯片制造厂提供),自动转换成门级网表。网表是由基本逻辑门(如与门、或门、非门)和触发器构成的电路连接图,是逻辑电路的物理实现蓝图。

- 门级验证与静态时序分析(STA):对综合后的门级网表再次进行功能验证。进行STA,在不依赖仿真的情况下,通过计算分析所有路径的时序,确保电路在指定的时钟频率下能够可靠工作,没有建立时间或保持时间的违规。

至此,芯片的“功能”和“逻辑”已完全确定,前端设计完成。

第二阶段:后端设计——绘制芯片的“物理地图”

后端设计,也称为物理设计,负责将门级网表转换成制造用的光刻掩膜版图,即芯片的“施工图纸”。

- 布图规划:就像城市规划,需要确定芯片核心面积、给各个功能模块分配位置、规划电源网络和时钟树的走向。好的规划能节省面积、提升性能、降低功耗。

- 布局:将网表中的所有标准单元(逻辑门的物理实现)和宏模块(如内存)精确地放置到芯片规划好的区域内。

- 时钟树综合:构建一个分布到所有时序单元的时钟网络,目标是使时钟信号尽可能同时到达所有端点,减少时钟偏移,这对芯片高速稳定运行至关重要。

- 布线:用金属连线将布局好的所有单元按照逻辑关系连接起来。这需要在数十亿计的连接中,避免短路、断路,并满足复杂的电气和时序规则。布线是后端最复杂、最耗时的环节之一。

- 物理验证与签核:

- 设计规则检查:确保版图完全符合芯片制造厂制定的工艺设计规则,否则无法生产。

- 版图与原理图对比:确保物理版图与原始逻辑网表在电气连接上100%一致。

- 最终的时序与功耗分析:基于实际版图的寄生参数(电阻、电容),进行更精确的STA和功耗分析,确保芯片性能达标。

所有验证通过后,生成最终的数据格式(通常是GDSII文件),交付给芯片制造厂。这份“蓝图”将被用来制作一系列的光刻掩膜版,通过光刻、刻蚀、离子注入、薄膜沉积等数百道复杂工艺,在硅晶圆上刻画出设计好的电路,经过封装测试,最终成为我们手中的芯片。

****

集成电路设计是一个高度依赖尖端EDA工具、严谨工程方法和跨学科知识的领域。前后端设计环环相扣,每一步都需经过反复验证,以确保这颗汇聚了数十亿甚至上百亿晶体管的复杂系统能够一次成功。正是这一系列精密的设计流程,支撑着摩尔定律的持续推进,不断将更强大、更智能的芯片带入我们的生活。

如若转载,请注明出处:http://www.fushanmingchuang.com/product/77.html

更新时间:2026-04-17 17:13:50