超大规模集成电路设计 技术、挑战与未来发展

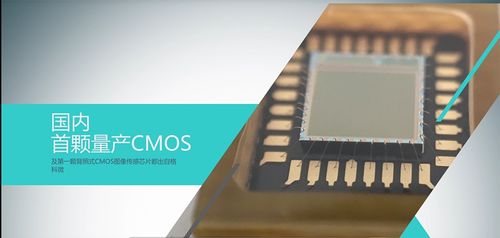

随着信息技术的飞速发展,集成电路(Integrated Circuit, IC)作为现代电子设备的核心,其设计复杂度不断提升。其中,超大规模集成电路(Very Large Scale Integration, VLSI)设计尤为关键,它涉及将数百万甚至数十亿个晶体管集成在单一芯片上。本文将从VLSI设计的基本概念、关键技术、面临的挑战以及未来趋势等方面展开讨论。

一、超大规模集成电路设计概述

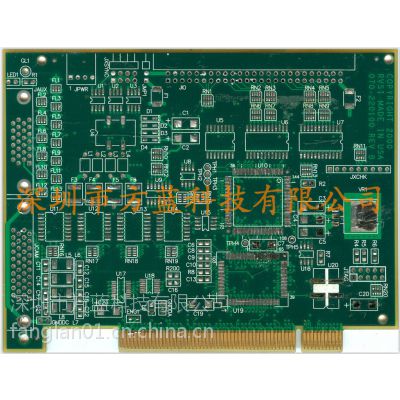

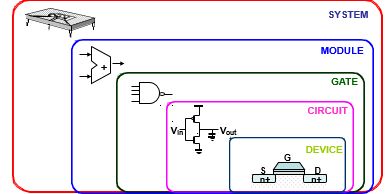

超大规模集成电路是指在单个芯片上集成超过10万个晶体管的电路设计。其设计过程包括系统架构设计、逻辑设计、电路设计、物理设计以及验证测试等多个阶段。VLSI设计的核心目标是在保证性能、功耗和成本平衡的前提下,实现功能的高度集成。

二、关键技术环节

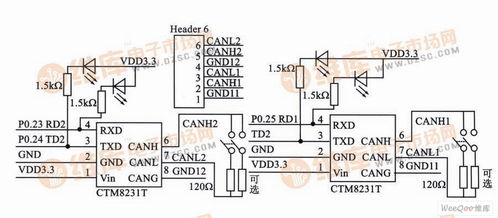

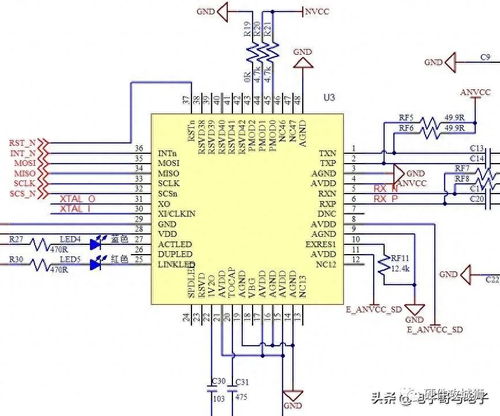

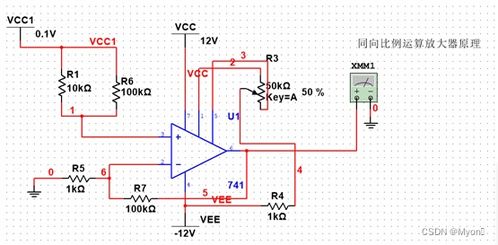

- 系统级设计:定义芯片的整体功能和架构,通常采用高级硬件描述语言(如Verilog或VHDL)进行建模。

- 逻辑综合:将高级描述转换为门级网表,优化逻辑功能和时序。

- 物理设计:包括布局(Placement)和布线(Routing),确保电路在芯片上的物理实现满足性能和面积要求。

- 验证与测试:通过仿真、形式验证和实际测试,确保设计的正确性和可靠性。

三、VLSI设计面临的挑战

- 功耗管理:随着集成度提高,功耗密度急剧上升,散热和能效成为关键问题。

- 信号完整性:高频信号易受串扰、延迟和噪声影响,需精细的信号完整性分析。

- 制造工艺限制:纳米级工艺下的物理效应(如短沟道效应)给设计带来不确定性。

- 设计复杂度:庞大的晶体管数量导致设计周期长、成本高,并需应对多学科交叉的技术难题。

四、未来发展趋势

- 人工智能与自动化:AI技术正被应用于设计自动化(EDA)工具,以优化布局布线和验证流程。

- 三维集成:通过堆叠芯片(如3D-IC)提升集成密度和性能,减少互连延迟。

- 新材料与新器件:碳纳米管、二维材料等有望突破硅基器件的物理极限。

- 异构集成:结合不同工艺节点的芯片,实现功能多样化与能效优化。

结语

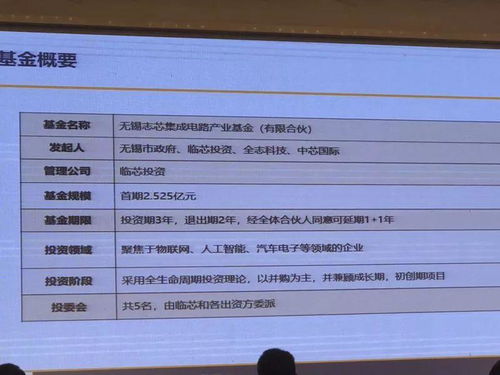

超大规模集成电路设计是推动信息技术进步的重要引擎。尽管面临诸多挑战,但通过技术创新和跨领域合作,VLSI设计将继续在人工智能、物联网和高速通信等领域发挥关键作用,为人类社会带来更智能、高效的电子解决方案。

如若转载,请注明出处:http://www.fushanmingchuang.com/product/34.html

更新时间:2026-04-15 13:49:15